In brief: Intel has revealed new information about its Xe Graphics Architecture at the company’s HPC Developer Conference in Denver, Colorado, ahead of the Supercomputing 2019 event.

We already know a few details about intel’s gaming-focused Xe GPUs, which you can read more about in this preview. Now, Intel’s SVP, Chief Architect and General Manager of Architecture, Raja Koduri has revealed the architecture roadmap for Xe and its product lines.

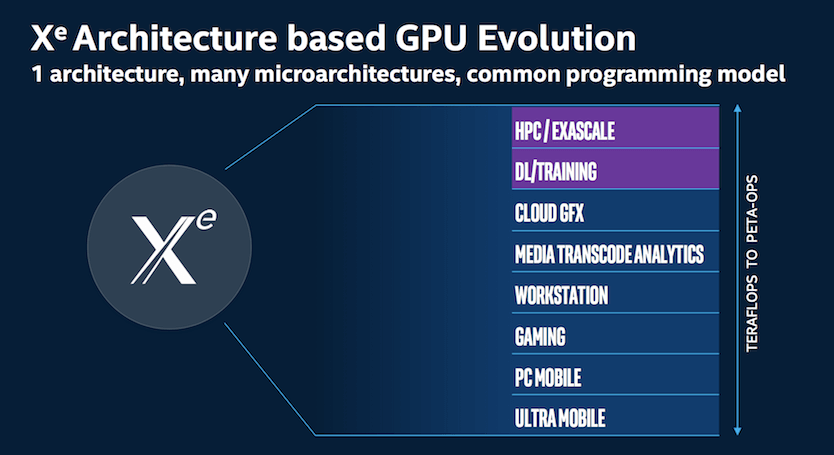

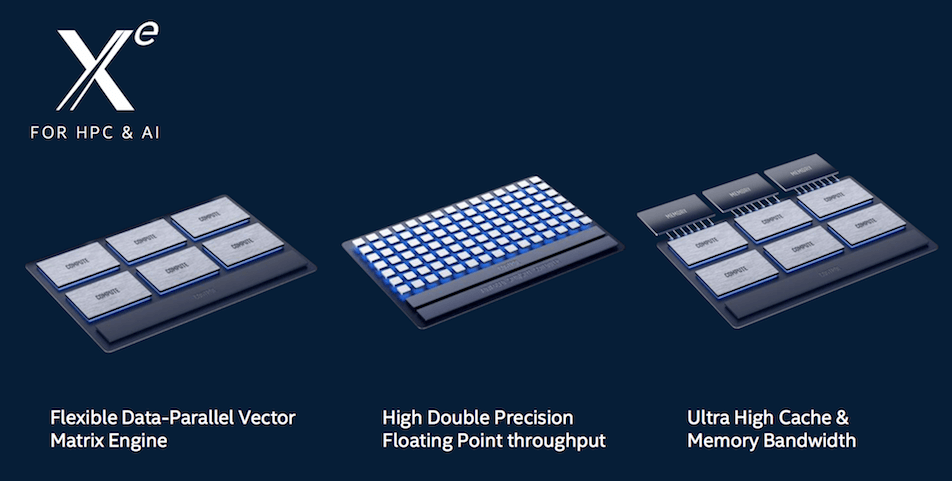

The Xe architecture will be offered in three designs: LP, for integrated graphics on processors; HP, which covers the mid-range, enthusiast, and datacentre/AI segments; and HPC for high-performance computing.

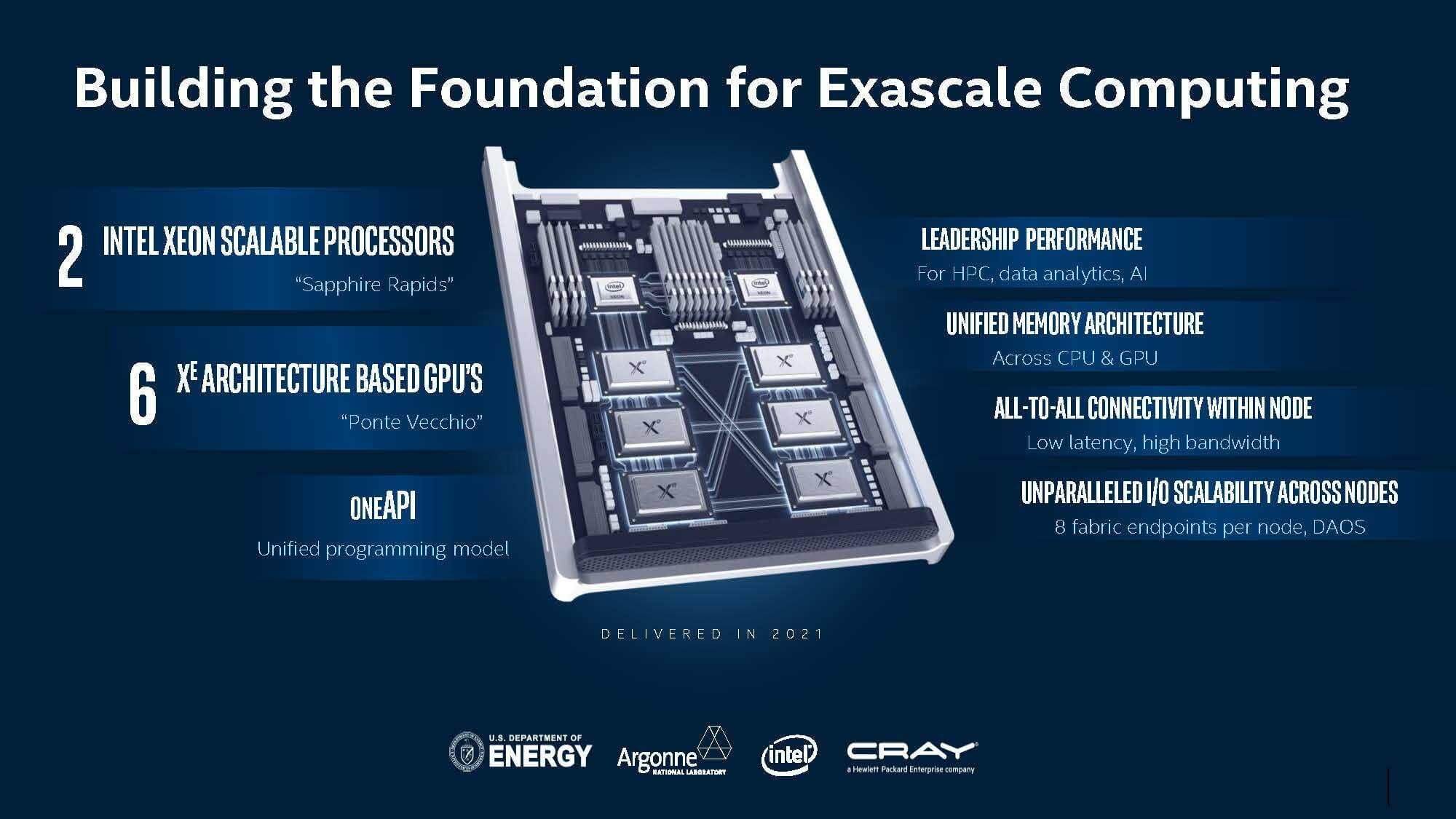

The first Xe Graphics Architecture for HPC and AI will arrive as the 7nm “Ponte Vecchio” graphics card. Intel calls it the company’s “first exascale graphics card,” and it will debut in the Aurora Supercomputer—the world’s first exascale computer—at the Argonne National Laboratory in 2021.

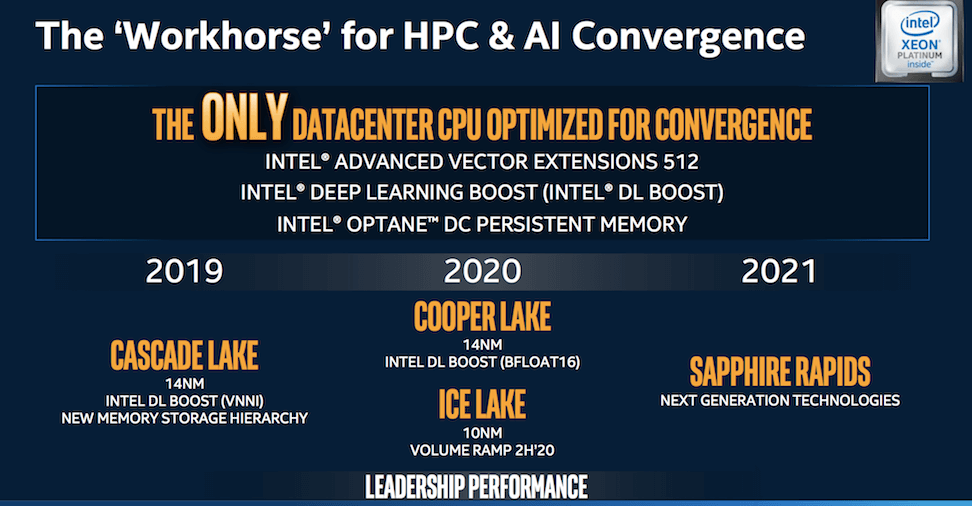

Intel revealed the node architecture of the Aurora system, which consists of two Xeon scalable processors called Sapphire Rapids, six Ponte Vecchio graphics units, and 16 compute units. The finished system will have more than 200 racks of servers, 230 petabytes of storage, and over ten petabytes of memory.

Intel chief executive Bob Swan said the company is “on track to launch our first 7-nanometer based products, a datacenter-focused discrete GPU in 2021.” Xe cards for consumer gaming will arrive next year, probably on 10nm.

Ponte Vecchio utilizes Intel’s Foveros technology, which uses a 3D-stacked die design that allows products to be broken up into smaller “chiplets,” where I/O, SRAM and power delivery circuits can be fabricated in a base die and high-performance logic chiplets are stacked on top. It also features EMIB (Embedded Multi-Die Bridge) tech, Compute Express Link interconnect, and other IPs.

The Xe HPC architecture also uses a large, unified cache called “Rambo,” which, when paired with Foveros, provides huge amounts of memory bandwidth to the GPUs and CPUs simultaneously.

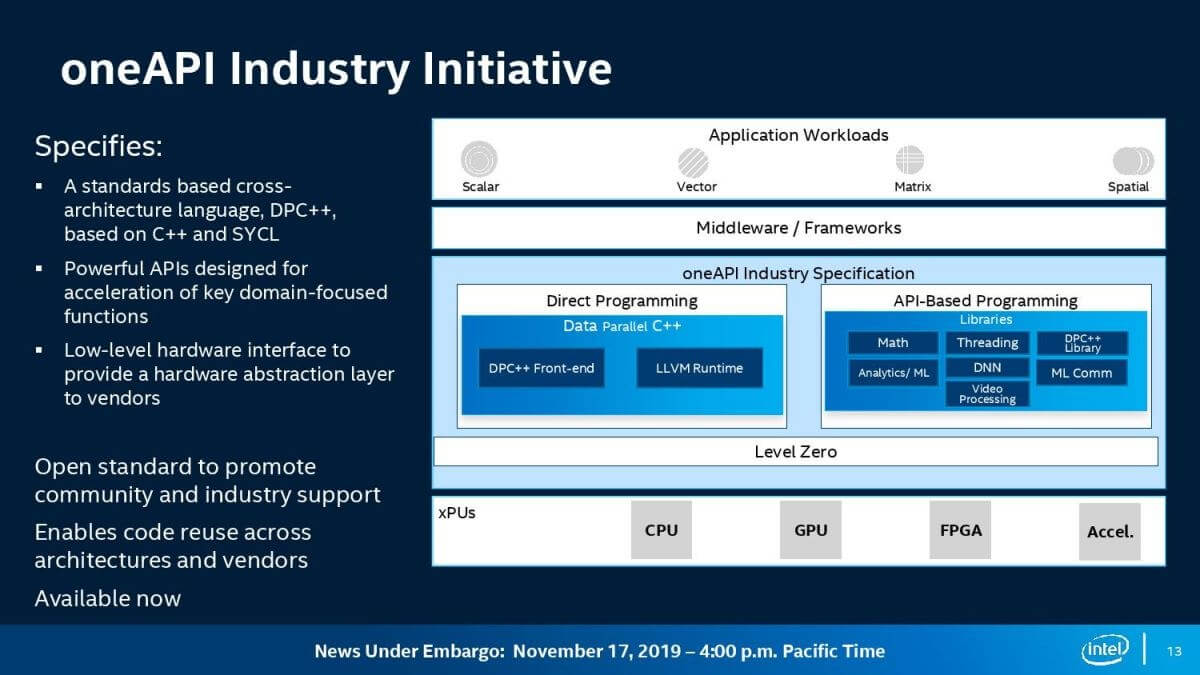

“HPC [high-performance computing] and AI workloads demand diverse architectures, ranging from CPUs, general-purpose GPUs, and FPGAs, to more specialized deep learning NNPs which Intel demonstrated earlier this month,” said Raja Koduri, chief architect at Intel, in a statement. “Simplifying our customers’ ability to harness the power of diverse computing environments is paramount, and Intel is committed to taking a software-first approach that delivers unified and scalable abstraction for heterogeneous architectures.”

Ponte Vecchio will use Intel’s OneAPI software initiative, which Intel says can “provide a unified and simplified programming model to deliver cross-architecture performance by allowing a diverse data-centric workload to benefit from the breadth of Scalar (CPU), Vector (GPU), Matrix (AI), and Spatial (FPGA) architectures”.

In its data center roadmap, Intel revealed the Sapphire Rapids processors, which are also expected to use the 7nm process node, would arrive in 2021. They are believed to support PCI 5.0 and feature eight-channel DDR5 memory.

Source link